-

回到頂部

-

400-1017-871

-

微信二維碼

聊聊 SSD 的基本原理

聊聊 SSD 的基本原理

大綱

數字化的存儲介質有很多。類似機械磁盤,固態盤,磁帶,光盤,等都是不同的介質而已。整個世界都在數字化,而數據就存在這些介質中。

存儲介質作為數字化的基石,它們的重要性可想而知,而近些年 SSD 的帶來的革命則更為深刻,原本毫秒、秒級別的時延被優化到微秒級別,幾百的 IOPS 優化到萬,十萬級別。這樣帶來的變化進一步影響軟件的變革,并且還在繼續。今天就簡單聊聊 SSD 的一些原理。

跟著我們先給自己預設一些問題:

SSD 的存儲單元是什么?

SSD 有沒有覆蓋寫?

順序寫和隨機寫的區別是啥?

SSD 非 4K 對齊的 IO 性能這么差?

希望這篇文章能給到你幫助。

你還記得機械盤嗎?大綱

大家都瞧不起機械盤 ,覺得性能太慢是技術能力不行?

其實機械盤是一種尖端技術,世界上只有那么兩三家公司(比如希捷,西數等)有能力生產機械硬盤,國內還沒這技術。也算是我們卡脖子的技術之一吧。不過好在 SSD 給了我們新的歷史機遇,可以迎頭趕上,甚至彎道超車也有可能。

它對比 SSD 為什么慢?

一個是機械運動,一個是電子的流動。這個速度差別可想而知。

SSD 一般是什么介質?

目前大部分的固態硬盤都是以閃存芯片為存儲介質。所以本文簡單默認 SSD 盤的介質就是閃存。

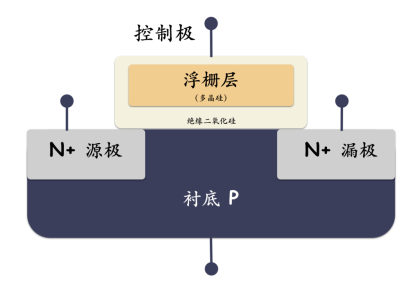

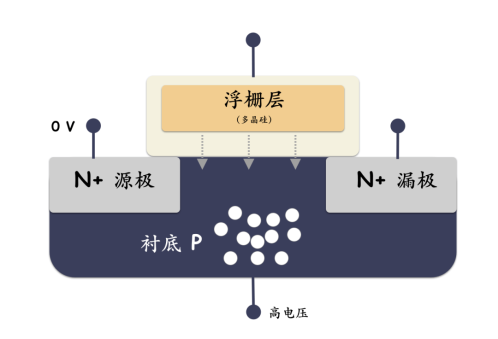

閃存的基本存儲單元是一種叫做浮柵晶體管的東西。于 1967年由華裔美國工程師施敏和韓裔美國工程師姜大元發明。浮柵管也屬于半導體晶體管的一種,浮柵晶體管太學術的原理這就不講。我們思考一個問題:它為什么可以作為存儲設備的單元?

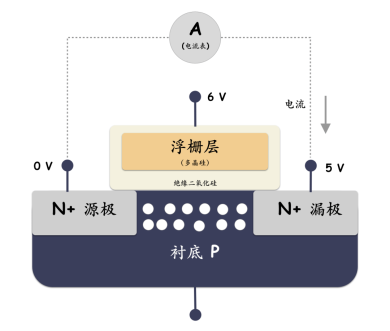

因為浮柵晶體管很特殊,它捕捉到電子之后可以保存起來數十年之久,電子保存在絕緣材料包裹的浮柵層中。示意圖如下:

1思考:為什么浮柵管可以作為是持久化的介質 ?

因為電子一旦進入浮柵層,就逃不出去了。掉電之后浮柵層的電子也不會消散。相當于就把狀態持久化下來。

2思考:閃存介質如何是標識 0,1 兩種狀態呢 ?

是否可以通過測量浮柵層里面有多少電子來判斷?

理論上好像可以。比如假定電子數量超過一個閾值就認為是 0,否則就是 1。但現實是電子數量非常難測量,所以我們通過另一種等價的方式來體現了 0 和 1,就是電流是否導通,也就是開關性。

浮柵層是否有足夠的電子能夠影響電路的開關,也等價標識了 0 和 1 的狀態。浮柵管就是這樣做的,具體來看一下。

給控制極加一個低壓,漏極加一個電壓。如果電流是導通的,那么說明浮柵層里是空的(或者說沒有足夠的電子),狀態為 1。如果電流不通,那么說明浮柵層里有足夠的電子,狀態為 0 。

注意,電壓數值都是為了具現化隨手拍出來的,并不是真實廠家的數值。一般閾值電壓都是廠家出廠前測出并設置好的的。

其中導通的原理是什么?

第一種情況:浮柵層是空的,沒多余電子(初始狀態)。

這個時候給控制極加一個低壓,漏極加一個電壓。這個時候,電子會盡量被控制極吸引,但由于電壓不夠擊穿絕緣層,所以就只是累積在N+源極和N+漏極之間,形成一條通路。

電子被漏極電壓吸引,進而流向源極形成通路。這個“電流導通”的狀態就表示 1 。

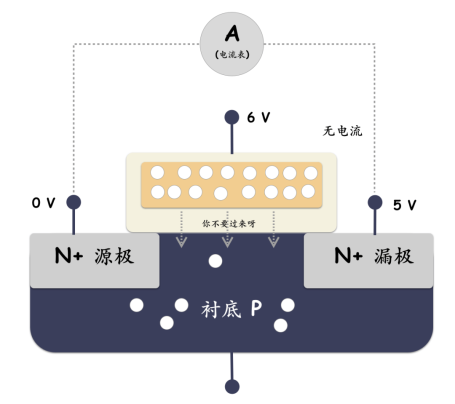

第二種情況:浮柵層有足夠電子(電子躍遷進來被捕獲的)。

浮柵層中如果有很多電子,那么它們會抵消掉很大一部分控制極對襯底里電子的吸引力。從而導致中間是一條斷開的路,無法形成電流。這種狀態表示 0 。

劃重點:漏極和源極如果導通標識為 1 ,不通為 0 。影響這個的因素就是浮柵層是否有足夠電子。

3思考:源極和漏極有啥區別?

物理結構上沒啥區別,它們就是對稱的結構。源極和漏極是以電子流動的方向做的劃分而已。電子從源極往漏極流動,電流方向相反。

高中物理:電流的方向和電子移動方向相反,電子往高電壓方向流動。

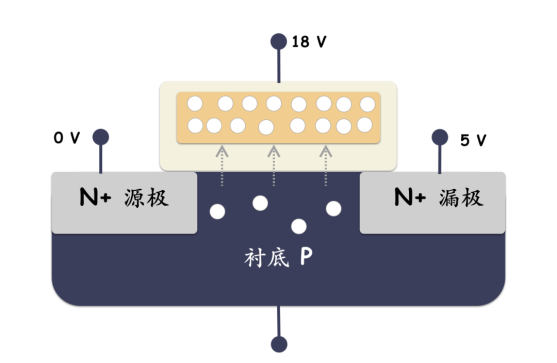

4思考:浮柵層的電子又是怎么來的呢 ?

頂部控制極加高電壓,就能把電子吸上來,往控制極流動。高壓的 吸引力會大到讓部分電子因為量子隧穿效應穿過絕緣的二氧化硅進入浮柵。請注意,進去之后就出不來了(完成持久化),除非襯底 P 加高電壓,原路徑把電子吸出來。

5思考:浮柵層捕獲電子是從 1 到 0 的過程,那從 0 到 1 的過程是怎樣?

從 0 到 1 的過程其實就是如何把浮柵層里的捕獲的電子掏出來。之前是在控制極加高電壓,讓電子躍遷到浮柵層,掏出來的話,自然是在相反的方向(襯底P)加高電壓嘍,讓電子重新吸出來。

6思考:為什么初始狀態 SSD 是全 1 數據?

因為浮柵層初始狀態是沒有電子在里面的,只有當電力驅動的時候,電子才能躍遷到浮柵層。所以初始化狀態是全 1 的數據。

SSD 的組織形式

閃存本質上是用電路的開關來表示 0,1 的狀態,所以本質上 SSD 怎么去組織這些存儲單元(浮柵晶體管),換句話說,就就是一個電路設計的事情。

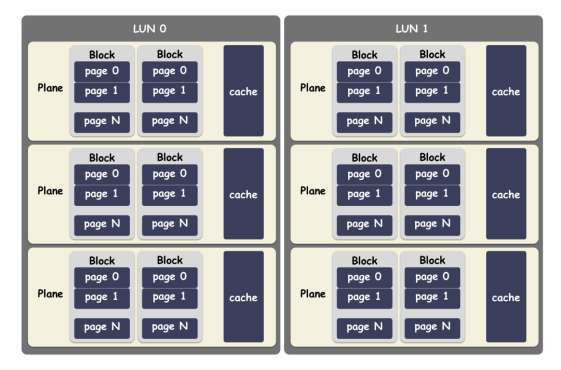

SSD 盤內部按照 LUN,Plane,Block,Page,存儲單元(浮柵管) 這樣的層次。不同的層次共用了不同的資源。整體的閃存內部的組織:

LUN 是接收和執行閃存的基本單元,換句話說,不同的 LUN 之間可以并發執行命令。一個 LUN 內,同一時間只能有一個命令在執行。

每個 Plane 有自己獨立的緩存,這個緩存是讀寫數據的時候用的。舉個例子,寫數據的時候,先把數據從主控傳輸到這個 Cache ,然后再把 Cache 寫到閃存陣列,讀的時候則是把 Page 的數據從閃存介質讀取到 Cache ,然后傳輸主控。

擦除的粒度是 Block , Block 里所有的存儲單元共用襯底。

SSD 盤 IO 的單元是 Page 。也就是說,無論是從閃存介質中讀數據到 Cache ,還是把 Cache 的數據寫到閃存介質,都是以 Page 為單位。

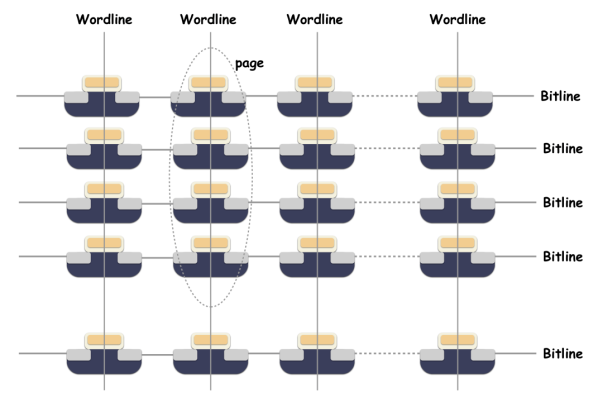

其實這里還有兩個概念,一個是 Wordline ,還有一個 Bitline 。這兩個概念得去看一下 Block的組織結構,很關鍵:

一個 Wordline 對應一個或多個 Page 。如果是 1 個 Page 那就是 SLC,2 個的是 MLC,3 個就是 TLC 。SLC 可靠性最高。一個 Block 中所有的存儲單元(浮柵管)共用一個襯底。

下面為了簡單,就只討論 SLC 的場景。

讀一個 Page 的時候,其實就是監測 Bitline 的導通性即可。

SSD 的讀寫擦的姿勢

SSD 以閃存為介質,閃存的存儲單元是浮柵管,但是讀寫擦的單元肯定不能以浮柵管為粒度,因為代價太大了。它們的操作粒度肯定是權衡出一個批量操作的值來,一次性操作一批。

1閃存的讀

2閃存的寫

3閃存的擦除

閃存的擦除就是把所有的存儲單元都恢復到初始狀態,也就是浮柵層里無電子,存儲單元全 1 的狀態。這個只需要在襯底加高電壓,電子就會從浮柵層吸出來。閃存的擦除以 Block 為單元。

思考

1閃存的擦除是以 Block 為單元的,為什么呢?

因為在電路設計上, Block 的所有存儲單元(浮柵晶體管)是共用一個襯底的(Substrate)。當對襯底施加高電壓的時候,那么所有的存儲單元浮柵層的電子都會被吸出來。電子吸出來,就是擦除的過程嘍。

2SSD 沒有覆蓋寫?

是的。從上面的設計來看,浮柵管的開關標識了 0 和 1 的狀態。數據的寫入是改變這個開關導通性,數據的讀取是監測這個導通性。SSD 盤的設計本質上是電路的設計,當前的電路設計上來講,無法做到直接在原地修改每個存儲單元的導通性。因為它的設計關聯到給誰加高電壓,給誰加低電壓。

所以最簡單的方法,就是給一初始狀態(全 1),然后把指定的位置加高電壓即可。這樣的設計應該是最簡單,成本上最可控。

3SSD 隨機寫和順序寫還有區別嗎?

如果是對一個 SSD 新盤來講,性能沒啥區別。但是讀寫久而久之就會有區別了,順序寫會導致需要擦除的 Block 比較集中,比較好處理一些。也更容易做讀寫的均衡。隨機的 IO 則會帶來更復雜的 GC 。所以它可能進一步影響后續的壽命,并且久了還可能影響性能。因為找到一個新 Block 的時間可能不一樣。

4非對齊的 IO 性能很差?

是的。IO 大小不按照 Page 對齊,那么可能導致 IO 的次數變多,可能會嚴重影響性能。你多一次 IO ,那么對整個盤跑滿來講,可能性能就降低一倍。IO 的放大還可能影響壽命。

總結

閃存的持久化狀態體現在浮柵層捕獲的電子,通過這個影響浮柵管的導通性來表示標識 0 和 1 的狀態;

浮柵層是否能關住電子就決定了 SSD 的壽命,如果它總是關不住電子,那說明它差不多到期了;

對浮柵晶體管的反復讀寫會影響它的壽命;

SSD 盤內部擦除的單元是 Block ,因為 Block 內部的存儲單元共用襯底;

SSD 盤 IO 讀寫的單元是 Page ,如果 IO 大小不對齊,那么會導致 IO 的放大,影響性能;

SSD 盤沒有覆蓋寫,永遠都是寫新的位置。這些新的位置都會是初始狀態(全 1 數據);

SSD 內部的垃圾回收來保證持續有新的 Block 可寫;

SSD 的隨機和順序 IO 寫影響更多的是 GC 的效率,從而影響壽命和性能